4

8051 Family Microcontrollers Instruction Set

Chapter Outline

- Learn programming basics and introduction to machine and assembly instructions

- Different types of instructions and addressing modes in the instructions

- Learn the data transfer, byte arithmetic and logic operation instructions of 8051

- Learn the data and bit manipulating Boolean processing, program control, IO and interrupt control instructions of 8051

- Write simple assembly language programs using 8051 instruction set

- Write simple programs for data transfer, delay and use of loops to understand the instructions

4.1 PROGRAMMING BASICS

A program means a set of instructions, which executes in an order. The order of execution of instructions is defined in the program. Many instructions in a program execute in a sequential order.

Each program has a start address. There is always the first executable instruction of program at the start address of a program. An end instruction can be for reset or halt or jump back to the same instruction or return (to the calling program or routine). The CPU fetches and executes from the start address the first instruction of a program or routine, then the next, then the next, and so on till the halt. Machine codes mean bytes that are fetched and executed by the CPU. Each memory address has 1 byte.

4.1.1 Machine Codes

A CPU recognizes only Is or Os. Every distinct instruction, which is executable on a CPU, has a distinct sequence of Is and Os in each byte of the instruction. A sequence of Is and Os is called a machine code. Each program consists of the instructions. The bytes that are saved in the memory for the instructions are called machine codes.

Consider the instruction for adding R1 into A registers. It is written as ADD A, R1 in mnemonic form. First source operand is R1. The second source operand is A. The destination is also A. It has a distinct machine-code 0x29 (also written as 29H to indicate that 29 is byte in hexa-decimal) of just 1 byte in 8051. (By convention, in 8051, the destination or the second source operand is written first and the first source operand next. Therefore, A is written first and R1 next after the ADD.) The instruction gives the result of adder operation in A and processor status, for example, carry C in PSW.

Assume ADD A, R1 is an instruction at address 0x4000. Since the instruction machine code is 29H (hexadecimal number for binary 0010 1001), the 0010 1001 saves as machine code at address 0x4000.

Example 4.2

Consider the instruction for jump to a long (16-bit) address 0x0100. It is written as LJMP 0x0100. It has a set of three distinct codes 02H 00H 01H at three addresses. (By convention, in 8051, the lower byte saves at the lower address and the higher byte is at higher address after the byte for the opcode. Therefore, 00H is first and 01H is next after the opcode 02H.)

The instruction is in the form of a byte (or bytes in case of longer than 8-bit instruction). A CPU first fetches a machine code from a memory address. It stores the code in IR (instruction register). It decodes the IR code. It then reads the operands of the instruction. Then that instruction executes. The fetch and execution steps for the machine codes of instructions are controlled by the controller and sequencing circuits (Fig. 3.1). The results are written after execution finishes. The CPU then fetches the new instruction for the next cycle of fetch-execute.

Each CPU on power up defines a start-up value of the program counter (instruction pointer). The CPU starts fetching the machine codes from that address. The start-up program counter value is 0x0000 (0000 0000 0000 0000b) in 8051.

Example 4.3

Assume that the initialization-program’s instructions (called boot-up program) start from 0x0100. Figure 4.1 shows the memory addresses in program memory and arrangement of the machine codes of the programs in 8051 in this case. The processor fetches the first instruction from 0x0000. Second instructions will be machine codes of boot-up program at address 0x0100. From then onwards the program’s instructions start executing. Figure 4.1 shows that first there will be machine codes at 0x0000, 0x001and 0x0002 for jump to 0x0100.

The reason that the boot-up program is starting from 0x0100 in the above example and not from 0x0000 is as follows:

- Between 0x0003 and 0x000A the 8 addresses should have machine codes for interrupt service routine for external interrupt INT0.

- Between 0x000B and 0x0012 the 8 addresses should have machine codes for interrupt service routine for external interrupt T0 overflow.

- Between 0x0013 and 0x001A the 8 addresses should have machine codes for interrupt service routine for external interrupt INT1 overflow.

- Between 0x001B and 0x0022 the 8 addresses should have machine codes for interrupt service routine for external interrupt T1 overflow.

- Between 0x0023 and 0x002A the 8 addresses should have machine codes for interrupt service routine for external interrupt serial interface TI (transmitter interrupt) and RI (receiver interrupt).

Figure 4.1 The memory addresses in program memory and arrangement of machine codes of the programs in 8051

Refer to Section 3.8 to find out why these addresses are used for interrupt servicing. After the interrupt service routines, there can be a blank space or constant data for program parameters up to 0x00FF. (0x00FF is the address just before the boot-up program at 0x0100.)

4.1.2 Program as a Set of Instructions and Routines

A program consists of a set of instructions. A program instruction may be for calling a routine (another program, a sub-program). A routine is another set of instructions at another set of start and end addresses. A program may also have a number of instructions to call the number of routines in between. A routine may also have an instruction to call another routine. A program or routine can also be interrupted and a new routine called ‘Interrupt Service Routine’ executes.

Routine: When an instruction calls a routine, the program counter for the next instruction I of the program saves and the CPU loads the program counter with the first instruction address of the routine. When the return instruction in the routine executes, the CPU loads the program counter for I.

Routine (subroutine) is a program or a sub-program. It is required by a program for executing a certain set of instructions. The CPU returns to the calling program instruction I after return. Each program or routine has the starting and end addresses. Figure 4.2(a) shows three memory areas for one program for an application and two routines for the same application. It shows three areas for the constants needed by these three as the input data.

Interrupt Service Routine: When an interrupt occurs, such as timer overflow, a new routine executes. That is called an interrupt service routine because it services (handles) the interrupt. Program counter for the next instruction of the present program saves and the CPU loads the program counter with the first instruction address in the new routine. When the return instruction in the ISR executes, the CPU loads the program counter back to enable previous program to run again.

Figure 4.2 (a) Three sets of the machine codes in three memory areas for one program for an application and two routines for the same application. Also shown are the three areas for the constants needed by these three as the input data. (b) Op-code and operands in four exemplary types of instructions

The program or routine or interrupt service routine, consists of a set of the machine codes stored as the bytes at the memory. The program runs by a sequence of executing codes.

4.2 INTRODUCTION TO MACHINE INSTRUCIONS AND ASSEMBLY

Programming in the form of machine instruction-codes is very difficult. The codes are in large numbers for the large number of instructions needed in a program. Therefore, programming can be done easily in the assembly form of the codes of the instructions or more easily in C language.

The following is a convention for the assembly format. Prefix 0x or Postfix H is used to indicate a hexa-decimal number, b to indicate a binary number and none to indicate a decimal number when writing an instruction. Destination operand in 8051 is written first after the operation specification. Prefix # is used to specify an operand, which is called immediate and is the succeeding byte(s) within an instruction.

Figure 4.2(b) shows the opcode and operands component in four exemplary types of the machine instructions. It is similar to an example tan 9. Here, tan defines the operation. It finds the tangent (ratio of perpendicular and base) to an angle. 9 defines the operand for the angle. Similarly, an assembly instruction has two components—opcode and operand(s). [Halt instruction has no operand.]

Instructions in assembly-language program are in the mnemonic form for the machine codes. Examples 4.1 and 4.2 give two mnemonics forms, ADD A, R1 and LJMP 0x0100.

4.2.1 Opcode

Each CPU defines a distinct set of instructions that distinguishes it from another CPU. It defines all the operations possible on that CPU. Therefore, each CPU has a distinct set of opcodes and one opcode for each distinct operation permitted by the CPU.

An opcode means the operation code.

Example 4.4

An operation may be as follows—add two registers and place the result back into one of the registers (ADD A, R5). Another operation could be add a register A with a constant number 8 (ADD A, #08). Both operations need distinct sequences of operations inside the CPU. Hence, both will have distinct opcodes for the ADD operation. One will have opcode for the add register into the accumulator and another for ADD immediate. Note that add-with-carry will have different op-codes and add-with-memory a different opcode. A and R5 are the operands in the first instruction and 08H is the operand called immediate operand in the second. The prefix # is an abbreviation for the immediate operand byte or number.

Example 4.5

Consider MUL AB. This is for multiplying the A and B register contents (bytes). It places the result into a set of two registers—A and B themselves. This instruction has the separate opcode from ADD registers or Add immediate. This is because MUL has a distinct set of CPU-operations. In this instruction, A and B are the source operands as well as the destination operand.

The CPU first fetches the code from an address. In fact, the byte fetched first is first examined for the opcode by the ID (Instruction Decoder). (The byte may have all the bits or few of the bits for the opcode.) Then, the code stores itself in IR so that the associated ID decodes it. Then only, the processing unit does the necessary operations using the controller and sequencing circuits (Fig. 3.1). The CPU operations after the opcode may also need subsequent further fetch of the operand(s)—the ones corresponding to the instruction in order to execute the instruction as per the opcode. It needs the program counter (which is also the instruction pointer) increment to change to another so that when all the CPU internal operations or actions are over, the CPU can fetch the next instruction from the newly pointed address by the program counter.

4.2.2 Operand

The CPU most often needs also the operand or operands in order to perform the operations as per the opcode. Let us consider that an opcode is for a transfer of the data byte from one register to another. Transfer means copy the bits. It is denoted by MOV in 8051 data transfer. Assume that opcode consists of just two bits and the instruction is MOV R1, R2. The 8051 instruction set convention is for specifying destination operand first and then the source. It means transfer (copy) R2 bits into R1.

- There is a need for an operand after the opcode for MOV instruction. That defines the destination where the data bits are to be moved, which actually means copied.

- There is a need of another operand. The instruction defines the source from where the data bits are to be taken. These registers are the ones usable by the programmer. (Source register R2 can be specified by three bits 010 if there are eight registers in the CPU. R1 is also specified by 3 bits010.) R1 and R2 are specified by 6 bits. Total instruction length is 2 + 6 = 8 bits (1 byte).

The total instruction code will consist of the opcode bits for register-to-register data transfer and two set of bits for the two operands. (Total of 8 bits (1 byte) is thus the instruction-length.)

The operations are performed on the source or sources. These are defined in the operands of the instruction. The result is saved at the destination, which is also defined by an operand. However, certain operands may be self-implied for an operation. Consider Example 4.1 ADD A, R1 instruction. The bits for representing R1 form one operand and the bits for the A form another operand. The third operand needed for defining the register A to place the result is self-implied by the CPU.

Example 4.6

Consider another operation for the SUBB A, #08H instruction (subtract-with-borrow and immediate 08H.) The bits for representing A form one operand and the bits for constant number 8H form another operand, called immediate operand because of the immediate availability of it as a succeeding byte in the instruction. The third source operand is carry flag. (Carry flag for addition is also used as borrow flag in 8051 subtraction). Fourth operand is needed for defining the destination register for the result. Both third and fourth (C in PSW and A) are self-implied in the CPU operation for SUBB.

The 2-byte instruction SUBB A, #08H consists of opcode bits for the subtraction with borrow immediate to register, and two set of bits for the two operands—one for the accumulator register and one for immediate.

4.2.3 Register

A register is a named entity. Each register in an MCU, or programmable-controller or device is assigned a name as per basic function(s) assigned to it in an instruction. P1 is a special function register in 8051. Its function is to function as input register and output register for the port P1 register. Consider two equivalent instructions in 8051—INC P1 and INC 90H. Both happen to be of 2-byte length and both increase the byte at P1 by 1. This is because in 8051, the direct address of P1 is 90H. However, when we write P1 in mnemonic form in place of 90H, it is easier to remember when programming. Operations possible on the registers are as follows:

- A register can store a variable or temporary variables that are directly and internally used by the processing units. A byte at a register has easy accessibility by the processor compared to the one at an external memory. External-fetch or store takes more time than an internal access by a processor. Consider the operation, a * b. A and B registers in 8051 store two temporary variables, a and b before the multiplication by MUL AB instruction or division by DIV AB instruction. MUL AB and DIV AB are just 1 byte long instructions.

- A large number of registers can load a larger number of program variables. The use of the registers greatly reduces the external memory accesses. The external accesses take a longer time than the internal accesses. 8051 has 32 registers distributed in four banks (sets).

- The number of register sets (banks or files) can load the variables in the different register sets in different tasks or routines or interrupt service routines. It greatly reduces the number of pushes and pops of the variables when the context switches on a call or interrupt. The 8051 has four banks (sets), and each bank can be assigned to separate routines or tasks. (The term context means a program’s present set of registers, program counter, stack pointer, A, PSW and other variables. When a program changes and another routine executes, we can say that the context has switched to another. When there is a return, we can say that the context has switched back. The term task is used in the operating systems. A task is a function the state of which is controlled by the OS and context switch from one task to another is also controlled by the OS.)

- A register can be assigned a specific action. For example, register A is assigned the role of an accumulator. It is also called ACC. ACC is used by the ALU in the accumulation of the result (for example, after increment, addition and logical operation). Consider 8051 instruction, SWAP A—it swaps (exchanges) lower and upper nibbles and the resulting byte accumulates in A itself.

- Each bit or set of bits of a register may have the specific and distinct action. Each bit of the n bits may be used together or separately. It all depends on the instruction. For example, statusregister (processor status word) bits in the MCU. Other examples are bits at (i) the mode register, TMOD (ii) the control registers, TCON and SCON.

- Each half (byte or nibble) of a register may have a specific and distinct action. Assume that the number of register bits is n. Then, n usually equals 8, 16 or 32. A register lower significance n/2 bits and higher significance n/2 bits may be usable simultaneously or separately in programming. It depends on the instruction.

- Each nibble or byte or 16-bit word or 32-bit double word in a register may have the specific and distinct action. Let n = 32. The lower significance n/2 bits, higher significance n/2 bits and two lower significances set of n/4 bits may be used together or separately. It will depend on whether an operand in the instruction is of 32 bits, 16 bits or 8 bits, respectively.

- A register can store a pointer (an indirect address or indirect address bits) for internal or external memory. Some examples make use of Ri and DPTR (DPH-DPL) in 8051. (Exemplary instructions are MOV A, Ri and MOVCA, A + DPTR). These instructions are explained later.

- When using a register, the few bits of operand suffice in the instruction. When using the register the instruction length may be shorter. When using a memory address in place of the register, the operand is of 8 bits or 16 bits for the address. For example, consider the register A. The 8051-instruction INC A is of 1 byte length. Now, consider an instruction INC direct with direct address—0E0H. The instruction length is 2 bytes. (The opcode is of 1 byte and address of 1 byte.) Both instructions are different but have equivalent actions except the number of times the program counter increments after the instruction executes. (In 8051, the direct address for A register is 0E0H.)

Figure 4.3 shows the many uses of a register during programming. A 1-byte register saves like a memory-address.

A programmer uses the registers in a large number of instructions. The use of a register differs from a memory in the following respects: Use of register makes the instruction-length small. When using memory the instruction-length is more. This is because address of the byte(s) in memory needs to be defined in the instruction. The increased instruction length increases the fetch-execution cycle time of the instruction.

Figure 4.3 Multiple uses of the registers during programming

4.2.4 Accumulator

A processing unit can be one address machine. It means that most instructions, particularly the ALU in-structions need only one operand definition in one address machine. The remaining operands are implicit. One address machine uses an accumulator. The accumulator (denoted by AC or ACC or A) is a processor register that accumulates result from an arithmetic or logic operation. Further, the accumulator also acts as the source operand in an instruction. Design of the processing unit with one address machine simplifies a processing circuit and internal control circuitry greatly. It reduces the maximum length as well as the number of the opcode bits in the instruction set. The programmer also finds it easy to assemble the codes. The accumulator can also accumulate a value from an external input port or memory and source a value to an external output port or memory. Examples are MOV A, P1 and MOVP1, A.

4.2.5 Program Counter

It is an address pointer for a code. It controls the flow of the program. It is abbreviated as PC in 8051. Right from the start of the processor, it always points to the next instruction to be fetched. During a task or routine, it usually increments continuously like a counter after fetching each byte of instruction. Figure 4.4 shows that the program counter changes to the next instruction address first. It takes a new value only on jump or call for another instruction or routine or return from a routine. It takes a default reset value on the reset instruction.

Figure 4.4 Program counter (or instruction pointer) initial values in 8051, 80x96, 80x86 and 80960 and the vector address for the program counter in 68HC11

- There is a default value that resets at start (power up). The value can be the same as the value on reset by hardware and software (for example, 8051) or can be distinct (for example, 68HC11).

- There are the distinct values at which it resets for the different interrupt vector addresses.

- A multi-process system will have multiple program counters and each process program counter has its distinct initial value. A multi-processing or multi-tasking or multi-threading system in a single-processor system will have multiple initial values of the program counter, distinct for each process or task. (The terms—thread, process and task are used in the operating systems. These are explained later in Chapter 11).

Figure 4.4 also shows the program counters’ initial values in 8051, 80x96, 80x86 and 80960. There is a vector address for the program counter value on reset in 68HC11. A programmer programs the 16-bit of the vector address. The program vectors to that value on reset on power up.

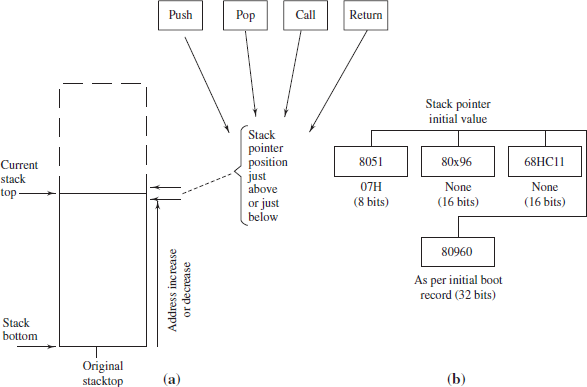

4.2.6 Stack Pointer

It is an address pointer for a memory address called stack top. It is abbreviated as SP in 8051. It is abbreviated as S in 68HC11. The SP points to a current stack top address. Stack is an important data structure. Data when saved (pushed) are stored in a manner that can be retrieved (popped) as last in first out (LIFO). The stack facilitates a programmer to save LIFO retrievable data. A stack is accessed from the memory in the LIFO mode, while a row of data in the queue is accessed in a FIFO (first in last out) mode.

Suppose, the processor saves the current program counter (calling program code address) onto the stack top, on return from the routine where the processor pushed that address earlier can be popped from the stack top and the program will switch back from the called program (routine) to the calling program.

- The SP increments (or decrements, depending on the processor design) after (or before, depending on the processor design) the push of each byte. Before a push, the pointed address at SP increases. Stack top is at the address 1 above the SP-pointed address in 8051.

- The SP decrements (or increments, in the processor design in which the push decrements it) before (or after, in the processor design in which during the push the SP change is before) pop of each byte. After a pop the pointed address at SP decreases in 8051.

- The memory addresses between the current stack top and original stack top at the start (stack bottom) hold the pushed bytes (for program counter or program variables or data) (Figure 4.5(a)).

- There may (for example, 8051) or may not (for example, 80x96 and 68HC11) be a default SP or S value which resets like the PC value on the start (power-up) in a processor.

- A multi-process system will have multiple stack pointers and each process stack pointer has its distinct initial value. A multi-process or multi-tasking or multi-threaded system in a singleprocessor system will have multiple initial values of the stack pointer for each process or task.

Figure 4.5(b) shows the stack pointer initial values and use during push and pop in 8051, 80x96, 80x86, 80960 and 68HC11. SP has 8 bits in 8051 default value = 0000 0111b (hexadecimal 07H), and 16 bits in 80x96 and 68HC11 (called register S in place of SP). S has no default values on the reset or power up in the processor. SP (stack pointer) has 16 bits in 80x86 and is used in conjunction with another register, called the segment register. 80960 has a 32-bit stack pointer called r1 register of the set of 16 local registers. ARM MCU uses r13 as the SP of 32 bits.

Figure 4.5 (a) Memory addresses between the current stack top and original stack top at the start (stack bottom) and (b) Stack pointer initial values and use during push and pop in 8051, 80x96, 80960 and 68HC11

4.2.7 Program Status Word

A processor or program status word register is one of the most important registers. It is abbreviated as PSW in 8051. It is invariably present in each processing unit for the programs.

A PSW has many bits. Either none or only a few pairs of bits may relate. A bit shows a certain condition of the process and so it is also called a flag. Carry auxiliary carry and zero flags are examples. Carry flag is used in all processors to implement multiple times addition or subtraction and there is use of carry (or borrow) in addition and subtraction. We can add or subtract multi-digit numbers multiple times by the carry. When a carry is generated in the arithmetic operation, the future arithmetic operation may depend on that. Therefore, the carry reflects the status of the process (or program). Note that the carry flag itself is used to show a borrow during subtracting.

An auxiliary carry flag is used in all processors to implement BCD additions. A condition that a carry results by addition of the lower nibble is saved in a bit called the auxiliary carry flag. A condition that a borrow results by subtraction of the lower nibble is saved in a bit called the auxiliary carry flag. Flag such as overflow is explained later.

Table 3.3 listed the P, OV, AC and C flags in 8051 PSW. Section 4.9 Table 4.8 lists the affected flags OV, AC and C in the arithmetic instructions. The logic operation instructions, AND, OR, XOR, INC and DEC do not affect the flags. Only RLC (rotate left through carry) and RRC (rotate right through carry) affect one flag, C. Parity P flag shows whether the number of bits in register A are odd or even (= 1 if odd). There is no zero flag. The programmer uses the PSW. 1 bit (least-but-one significant location bit the PSW) as the user flag F1. The programmer uses the PSW.5 bit (highest-but-two significant location bit the PSW) as the user flag F0. F0 and F1 can be used in the program to reflect the task statuses. For example, it can be used to test whether the modem is interfaced to the MCU. Another example is to find whether a control task is active or inactive. These flag programs can be used to let one of the tasks execute as per the status of other tasks. F1 and F0 can be tested by another instruction during a program control task in a multi-tasking system. (Chapter 11 will describe multitasking operations.)

PSW.4 and PSW.3 are RS1 and RS0 (register set bits). There are four sets of registers with 8 registers in each set. The use of 8 variables per task is often sufficient in a program. RS1–RS0 reflects the status, where program register-set is in use.

Suppose a program has four tasks—tasks 0, 1, 2 and 3. The variables of task 0 can be stored in register set 0 when RS1 and RS0 are 00. We use two instructions CLR PSW.4 and CLR PSW.3 instructions at the beginning of program task 0. The variables of task 3 can be stored in register set 3 when RS1 and RS0 are 11. We use two instructions SETBPSW.4 and SETBPSW.3 at the beginning of program task 3.

A task may consist of the codes for a single routine (or function) or the multiple routines (or functions). In the absence of use of different register sets for the different tasks, a program needs to push the variables in the registers onto the stack before switching from one task to another and pop from the stack back on switching back (return) to the task.

A register set is also called the register bank. The programmer definition of RS1-RS0 bits in advance. This helps in shortening certain future program instructions from 2 or more bytes length to 1 byte length.

For example, MOV A, Rn instruction is just 1 byte length. It means move into A the bits at n-th register of the register bank specified by RS0-RS1. MOV A, direct where direct is the address for the variable in an Rn, is 2 bytes length.

4.2.8 Assembly and Machine, Assembly and C Instruction Formats

The codes are in large numbers for the large number of instructions needed in a program. Appendix G gives the machine codes for the 8051 instructions in mnemonics form. Figure 4.6 shows a set of instructions for finding x = (a + b + c) × d in three formats—machine code, assembly and high-level language. High-level format has just one line, assembly format seven lines in 8051 and nine machine codes for an exemplary calculation for x.

Figure 4.6 Exemplary nine machine codes, seven assembly codes and single high-level C language expression

Consider C langauge statement x = (a + b + c) × d. It implies the following:

- Take the number from address of b, add it in the number at address a.

- Take the number from address of c, add it in the number at address a.

- Take the number from address of d, multiply it in the number at address a.

- Put the result at the address of x.

Assembly language has seven instructions for the above statement; assume the following—the address of a is R0, address of b is R1, c is R2 and d is R3. It assumes the result x of 16 bits in R4 and R5. The operations by the instructions are as follows:

- Move R0 into A.

- Add R1 into A.

- Add R2 into A with carry generated in the previous addition operation

- Move R3 into B using direct address F0H for B.

- Multiply A and B (multiplication instruction is available for the multiplication of A and B not with A and R3).

- Move the lower byte as a result of multiplication in A into R4.

- Move the higher byte as a result of multiplication in A and B into R4 and R5. Use direct address F0H for B.

There are nine machine codes for the seven instructions in the assembly. We use the table in Appendix G for finding the machine codes for the instructions and SFR address F0H for B.

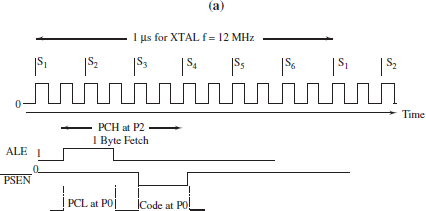

4.3 INSTRUCTION CYCLE

An instruction cycle is the cycle in which the steps take place for fetching an instruction (including fetching of needed operands) and for executing the instruction. Figure 4.7 shows an instruction cycle. It is measured in cycles. An instruction needs a minimum of one cycle. ADD A, R5 needs one cycle. ADD A, #08 also needs one cycle in 8051. MUL AB needs four cycles. A cycle takes 1μs period when XTAL frequency in MCU is 12 MHZ. This is because a cycle has six states, S1 to S6, and each state has two clock pulses (Fig. 3.7). MOVXA, DPTR is an instruction to move (transfer or copy) contents from the external memory address pointed by the DPTR 16 bits. It takes two cycles, each of six states.

Figure 4.7 Timing diagram of instruction cycle for fetch operation in S1, S2 and S3 clock states if the length of the instruction is 1 byte

A timing diagram in Fig. 4.7 shows that if the length of instruction is 1 byte, it is fetched during S1, S2 and S3 states. Time is on horizontal axis. Logic state is on vertical axis. It shows at the bottom the durations for the PCL at P0 and code P0. Figure 4.8 shows that a 2-byte instruction is fetched during S1 to S6. Figure 4.9 shows that 3-byte instruction is fetched during nine states (first instruction cycle and half of second instruction cycle). The tables given in the following sections will also give the instruction lengths in bytes and the cycles to complete fetch and execute of each instruction.

Figure 4.8 Timing diagram of an instruction cycle for the fetch operation in S1 to S6 states if the length of an instruction is 2 bytes

Figure 4.9 Timing diagram of instruction cycles for the fetch operation in S1 to S6 clock states of the first instruction cycle and S1 to S3 of the second cycle if the length of the instruction is 3 bytes

4.4 EXECUTION TIME OF AN INSTRUCTION

Instruction cycle helps in estimating the time needed for executing an instruction. Adding the total number of instruction cycles in a program that will take during execution gives the total time required for the instruction.

For example, a two-cycle instruction will need 2 μs in 8051. This is because a one-cycle frequency is (1/12) fosc, where fosc is the XTAL oscillation frequency.

Example 4.7

Find the time taken in the following seven instructions. Assume 12 MHz Xtal with 8051. Use the number of cycles given in the tables for the instructions in Tables 4.1 and 4.8.

- MOV A, R0 takes 1 cycle (Table 4.1)

- ADD A, R1 takes 1 cycle (Table 4.8)

- ADDC A, R2 takes 1 cycle (Table 4.8)

- MOV B, R3 takes 2 cycles (Table 4.1) [It is MOV direct, Rn instruction where n = 3 and direct is the address 0F0H of B.]

- MUL A, B takes 4 cycles (Table 4.8)

- MOV R4, A takes 1 cycle (Table 4.1)

- MOV R5, B takes 2 cycles (Table 4.1)

Total number of cycles = 12 cycles. Time taken = 12 μs.

4.5 ADDRESSING MODES

An addressing mode is a method of specifying the data source or destination in an instruction. Figure 4.10 shows the various addressing modes. (Modes in dotted boxes are present in the other CPU families’ instructions.) The modes in the 8051 family instructions are as follows:

- Immediate: The data bits for instruction are a part of the instruction and are the next byte after the opcode.

Figure 4.10 Addressing modes (dotted box modes are the modes present in other CPU families)

For example, in ADD A, #08 the addressing mode is called the immediate addressing mode, because the source operand is the immediate (next succeeding) byte in the instruction. (Destination immediate addressing is not logical and hence not permitted.)

- Register: In this, the data bits for instruction are at a register(s). This is specified by the operand bits in the instruction. ADD A, R5 addressing mode is called the register-addressing mode, because the source operand is the register specified in the instruction.

- Direct: The address of 8-bits is directly specified in the instruction. Instructions for the SFRs have only the direct-addressing mode in 8051. Internal RAM between 0x00 and 0x7F is also accessible by direct addressing.

Example 4.9

For example, MOVR5, 90H (MOVR5, P1 for source at the SFR for P1 port. P1 has the address 90H).

Example 4.10

MOVR5, 0F0H (MOVR5, B. Source operand is SFR B. Direct address of B is 0F0H. A convention in assembly programs is to prefix 0 before a hexadecimal digit A or B or C or D or E or F so that the digit is not taken as a register).

Example 4.11

MOVR5, 3CH. Move the byte into R5 from internal RAM address 3CH.

The mode is called direct address mode because the source operand is from the address specified in the instruction.

Note:

- MOV R5, #90H will have a different mode. It moves the immediate operand into the R5. # sign specifies immediate operand as the source.

- Many direct addresses between 0x80 and 0xFF do not exist as there are much less than 128 SFRs.

- Indirect register (Indexed): The address (of 8-bits) is indirectly specified in the instruction by the contents of a pointer. Consider MOV A, R1. Here, MOV into A register the byte from the address pointed by the contents of R1. R1 and R2 are used as address pointers in 8051.

Example 4.12

Assume that R1 has byte 80H (pointer for Port P0 SFR address). MOV A, R1 transfers the byte from P0 using R1 as an indirect pointer for address. The addressing mode is so called because the source operand is from the address specified indirectly by another register in the instruction.

Example 4.13

8051 has a 16-bit register DPTR that works like a base register and points to an external memory address.

Example 4.14

68HC11 has two index registers, X and Y. Each one is of 16 bits. Either X or Y can be used along with an offset (displacement) bit defined in the instruction. Assume X points to a base address for the first rows first column of a table. X + Y can point to any row-first column addresses. The Y plus offset can point to any column in the row. Therefore, any table element address is X + Y + offset. Here, offset = displacement from the first column to the current column. Displacement is the address difference and is specified at the instruction.

Instructions for the internal RAM between 00H and 07FH have the indirect addressing mode also in 8051 in addition to the direct address mode. Instructions for the internal RAM between 80H and 0FFH have only the indirect addressing mode in 8052. (A convention in assembly programs is to prefix 0 before a hexadecimal digit A or B or C or D or E or F so that the digit is not taken as a register.) Internal RAM between 80H and 0FF (when present) is only accessible by indirect addressing.

Note:

- Direct addresses between 80H and 0FFH for the internal RAM area does not exist as there is SFR area at these addresses and SFRs are direct address accessible and therefore indirect address-specifying register must have the valid internal RAM address. For example, address 93H is valid in 8052 and invalid in 8051.

- Only R0 and R1 in a register bank are used in 8051 for indirect addressing.

- Bank for R0 or Bank for R1 depends on the RS0 and RS1 bits at the SFR PSW.

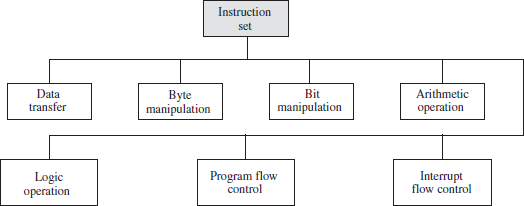

4.6 CLASSIFICATION OF THE INSTRUCTIONS AT THE INSTRUCTION SET

Instruction set of a CPU can be classified into the following. Figure 4.11 shows a classification of the instructions in the instruction set. (Appendix G gives the 8051 instruction set.)

It is as follows:

- Data Transfer Instructions

- Boolean Variable Manipulation Instructions

- Arithmetic Instructions

- Logic Instructions

- Program Flow Control (Processor and Machine Control) Instructions

- Interrupt Flow Control Instructions

Figure 4.11 Classification of the instructions in the instruction set

4.7 DATA TRANSFER INSTRUCTIONS

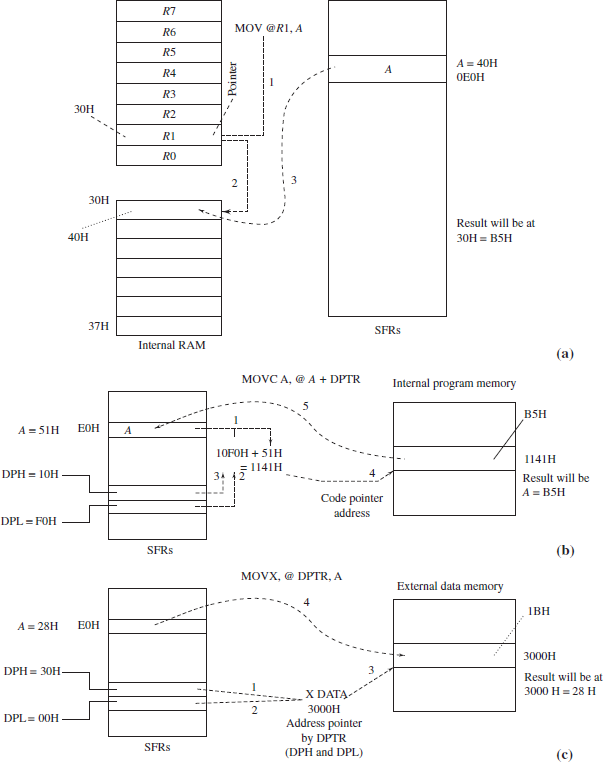

The 8051 instruction set has three types of the data transfer by move instructions. Transfer within the internal RAM and SFRs is of one type. The second type is transfer using code memory area (CODE and CONST). The third is using the external data memory (X-DATA). Figures 4.12(a)–(c) show the sequences in operations for data transfer instruction when using MOV, MOVC and MOVX instructions, respectively.

4.7.1 MOV Instructions

A MOV instruction means move (copy) the bits from one source to a destination. The 8051 MOV instructions are given in Table 4.1.

Table 4.1 MOV instructions within the registers, internal RAM and SFRs in 8051

a n is 0 or 1 or … or 6 or 7 for a register in the register bank. The bank is defined by RS0 and RS1 bits at PSW.

b Data bits of the byte to be moved.

c Direct is the byte for the address from where the byte at that address is to be moved. The address should be valid (existing SFR) in the SFR area or should be between 0x00 and 007F.

d i = 0 or 1. Byte to be moved from the address pointed by the contents of Ri. Prefix @ implies a pointer register. R0 or R1 can be a pointer register in a bank. The bank is defined by the bits RS0 and RS1 at PSW.

e Data of 16-bits to be moved into the DPTR. The DPTR is in two SFRs at the addresses 83H for DPL and 84H for DPH. Two direct addressing instructions will be needed if both are independently written.

One of the most important uses of MOV instructions are programming of the SFRs. Some examples are MOV into (i) TMOD and TCON for timer, or (ii) SCON for the serial interface device, or (iii) setting the interrupt masks in IE or (iv) set interrupt servicing priorities in IP. The second most important advantage is reading (moving) into a register the SFR SBUF serial input bits or moving the bits at the port into specified register (Rn) or reading internal RAM.

Example 4.15

Write the control bits 0100 0000 (40H) into the TCON.

TCON is an SFR. and it is in the direct-addressable space. TCON address is 88H. Instruction MOV direct, #data is there in Table 4.1. Using that the MOV TCON, #40H will be the instruction to write into the TCON.

Example 4.16

Load the external memory address pointer DPTR with 0x1000 (1000H). There is an instruction MOV DPTR, #data16 (Table 4.1). The instruction is, therefore, MOV DPTR, 1000H.

Example 4.17

Load 0x1000 (1000H) in DPTR. Write instructions using the DPL and DPH as the 8-bit operands.

Alternatively for the instruction MOV DPTR, #0x1000 we can use the fact that DPH and DPL are the SFRs at addresses 83H and 82H, respectively. There is MOV direct, #data instruction (Table 4.1). Instructions are as follows:

MOVDPH, #10H and MOVDPL, #00H or MOV83H, #10H and MOV82H, #00H.

Figure 4.12(a) shows three steps for instruction MOV @R1, A. This is an indirect addressing mode instruction. First step: R1 is read by the processing unit. Second step: pointed address 30H is found from R1. Third step: A is read and its contents found = 40H and 40H is transferred (copied) to address 30H from A.

Figure 4.12 (a) Three steps for MOV @R1, A. The 40H moves to address 30H, which is pointed by Ri (b) using MOVC the B5H moves from 1141H into A (c) MOVX instructions the 28H moves into X-Data memory address 3000H

How can a byte be transferred from the address pointed by R0 to the register R2? There is no MOV @ Ri, Rn instruction available.

MOV @Ri, Rn is not an instruction present in 8051 but MOV Rn, A and MOV A, @Ri are available (Table 4.1). Hence, the byte pointed by R0 can first be moved into A and then to R2. The instructions are as follows:

MOV A, R0 and MOVR2, A to transfer a byte from the address pointed by R0 to the R2.

4.7.2 MOVC-type Instructions

An MOVC instruction means move (copy) the 8-bit code from one source at the program memory (internal or external) to the register A destination.

Figure 4.12(b) shows four steps for instruction MOVCA, @A + DPTR. This is an indirect addressing mode instruction. First step: 51H at A is read by the processing unit. Second step: pointed address lower byte DPL and higher byte DPH are read. Third step: DPH-DPL 16 bits 10F0H and 51H are added. The result 1141H is used as a pointer in the next step. Fourth step: 0B5H at the program memory address 1141H is transferred (copied) into A. A now has 0B5H.

The 8051 MOVC instructions are given in Table 4.2. These instructions are particularly important for accessing the constants (Table 2.2) in the program memory.

Table 4.2 MOVC instructions for transfer from the program memory area address code or constant to the accumulator in 8051

a DPTR does not change and is the base address. Address is relative to DPTR with index (offset) at A.

b PC does not change and is the base address. Address is relative to PC with index (offset) at A.

Another use of instruction MOVC is that it can be used to copy the codes from one set of memory area to another during the development phase. After the development phase is over, in certain 8051 MCUs there is a provision to disable its use by a security bit so that the internal program memory area cannot be copied later.

Example 4.19

Assuming PC to be 1000H, transfer the code at 1000H to the internal RAM at 70H.

For transferring the codes, the MOVC A, @A + PC is there in Table 4.2. First, we load A with 00H (Table 4.1). Then, we use the MOVC instruction to first get the code into A. From A, we can load it into adderss 70H.

(i) MOV A, #00H; (ii) MOVC A, @A+PC; (iii) MOV 70H, A; to read the code at 1000H into 70H.

Using DPTR, transfer the codes from 1000H and 1001H to addresses 7EH and 7FH in RAM.

For transferring the codes, the MOVCA, @ A + DPTR is there in Table 4.2. First, we load DPTR with 1000H and A with 00H (Table 4.1). Then, we use the MOVC instruction to first get the code into A, from where we load it into 7EH.

(i) MOV DPTR, 1000H; (ii) MOV A, #00H; (iii) MOVC A, @A + DPTR; (iv) MOV 7EH, A; to read the code at 1000H into address 7EH.

With DPTR already loaded, move 01H into A and use MOVC instruction again and move A to 7FH: (v) MOV A, #01H; (vi) MOVC A, A + DPTR and (vii) MOV 7FH, A ; to read the code at 1001H into 7FH.

4.7.3 MOVX-type Instructions

A MOVX instruction means move (copy) the 8-bit data into A and from A using the external data memory addresses using DPTR or Ri as the pointer.

Figure 4.12(c) shows four steps for instruction MOVX @DPTR, A. This is an indirect addressing mode instruction. First step: Pointed address lower byte DPL is read. It is 00H. Second step: Pointed address higher byte DPH is read. Third step: DPTR points to address 3000H. Fourth step: 28H at A is transferred (copied) into data memory at address 3000H. Data memory 3000H address now has 28H.

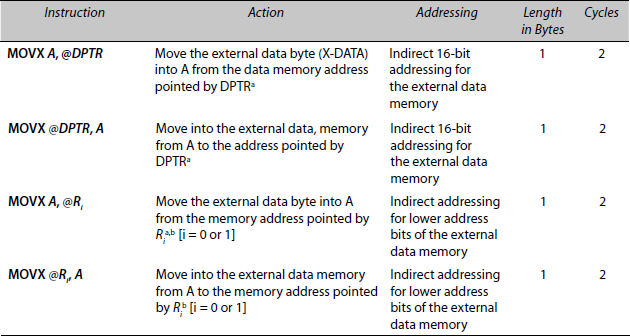

The 8051 MOVX instructions are listed in Table 4.3.

The advantage of a separate MOVX is that it can be used to copy the bytes from or to using the external RAM for the data memory for X-DATA between 0000H and FFFFH.

Example 4.21

Using DPTR, transfer the codes from 1000H and 1001H to external data memory addresses 1000H − 1001H to show how we copy the codes from code memory in ROM to the external RAM.

For transferring the codes into A, the MOVC A, @A + DPTR is available (Table 4.2) and for the from A to external data memory, the MOVX @DPTR, A is available (Table 4.3). First, we load DPTR with 1000H and A with 00H (Table 4.1). Then, we use the MOVC instruction to first get the code into A.

(i) MOV @DPTR, 1000H; (ii) MOV A, #00H; (iii) MOVC A, @A + DPTR; to read the code at 1000H into A. DPTR is already loaded. From A, we can store the byte into external data memory at 1000H because DPTR = 1000H and we can use MOVX @DPTR, A. Therefore instruction (iv) MOVX DPTR, A is used.

Now, for saving the next code at the next address, we can perform the operations as follows:

(v) MOV DPTR, 1001H; MOV A, #00H; (vi) MOVC A, @A + DPTR and (vii) MOVX @DPTR, A; to read the code at 1001H and write into XDATA data memory 1001H.

Table 4.3 MOVX instructions for the transfer of 8-bit data into A and from A using the external data memory addresses using DPTR or Ri as the pointer in 8051

a DPTR (DPH and DPL together) has the 16-bit address for the external memory.

b Indirect 8 lower bits address for the external data memory defined at Ri. Upper bits are taken as 00000000b. Therefore, when the X-DATA memory address is between 0000H and 00FFH, the R0 and R1 can be used.

4.7.4 PUSH and POP Instructions for Using the Stack Area Employing the SP

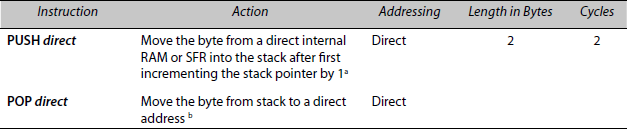

PUSH instruction means move (copy) the 8-bit data into the stack after incrementing SP. The data are at a direct address. The address is of either an SFR or internal RAM between 00H and 7FH. Table 4.4 lists 8051 PUSH and POP instructions.

Table 4.4 PUSH and POP Instructions in 8051

a Stack pointer SP in 8051 is of 8 bits. 8051 Push instruction first increments the SP and then pushes the byte.

b Pop instruction pops the byte and then decrements the SP. Therefore, the initial value is always kept low, for example, 0x07, in place of 0xFF. (Default SP at startup is also 07H.) However, there is internal RAM and stack area overlap. We can set the initial value of SP as 7FH in the 8052 family, the PUSH will be only in the indirectly accessible area between 80H and 0FFH starting. Push is then at 80H and above. Therefore, the POPs will also the restricted to this area between 80H and 0FFH.

The advantage of the PUSH instruction is that the values in the registers, RAM or SFRs can be saved for the LIFO operations later. Some array values can be dumped on the stack and can be retrieved later as LIFO. For example, when we are arranging the values in the ascending order or in descending order.

Another advantage is that a variable of 1 byte can be saved at the stack temporarily by a PUSH.

An accumulator is used in a number of instructions. How will we save the value of A and retrieve when needed?

Table 4.4 shows that only PUSH direct instruction is available. We use PUSH 0E0H. A’s direct address is 0xE0.

Use of Stack to Save the Accumulator and Processor Status Word

Example 4.23

When using an ISR sometimes, there is need to save A and PSW on the stack. This is to make A and PSW available for use in the ISR. Before the last instruction return from the ISR, there is need to get the saved A and PSW back.

A register direct address is 0xE0 (=E0H). PSW register direct address is 0x0D0 (=D0H). We use PUSH 0E0H and PUSH 0D0H. We simply use PUSH A and PUSH PSW in case we are using an assembler, which will automatically place the direct addresses of A and PSW in the codes.

Note that we are using the default value SP here. Else, we can initialize SP by using MOV SP, #data or MOV81H, #data because 81H is direct address of SP.

Now, when needed, the stack-saved value can be retrieved by POP PSW and POP A.

Use of Stack to Save Registers at a Bank

Example 4.24

Assume that R0 to R7 have the array values in the ascending order. Assume register bank 0 is used. Rearrange these in the descending order.

We can use the LIFO property of the push and pop stack operations as follows:

(i) PUSH 00H; instruction to save R0 (note that PUSH R0 is not an instruction); (ii) PUSH 01H; (iii) PUSH 02H; (iv) PUSH 03H; (v) PUSH 04H and (vi) PUSH 05H; (vii) PUSH 06H; (viii) PUSH 07H; (ix) POP 00H; (x) POP 01H; (xi) POP 02H; (xii) POP 03H; (xiii) POP 04H; (xiv) POP 05H; (xv) POP 06H; (xvi) POP 07H;

Use of Stack to Save A and SP

Example 4.25

(i) Write 00H at Port P0, P1, P2 and P3 using POP instructions and using MOV A, #00H and PUSH 0E0H (equivalent to PUSH A). There should not be any effect on A and SP at the end of the instructions. (Use default SP of 07H.) (ii) How will we check that the SP remains unchanged at the end of a set of the instructions in a program?

First, let us save A and SP. (i) PUSH 0E0H (ii) PUSH 81H (equivalent to PUSH SP as the SP direct address is 81H); now, use MOV immediate, push and pop instructions to write into P0, P1, P2 and P3. (iii) MOV A, #00H; (iv) PUSH 0E0H; (v) POP 80H(equivalent to POP P1); (vi) PUSH0E0H; (vii) POP 90H (for popping into P1); (viii) PUSH 0E0H; (x) POP 0A0H(for popping into P2); (xi) PUSH 0E0H; (xii) POP 0B0H (for popping into P3). Restore SP first as it was pushed after A in instruction and restore A later; (xiii) POP 81H (equivalent to POP SP) and (xiv) POP 0E0H (equivalent to POP A) instructions first restore SP and then A from the stack.

We also check whether the SP does not change at the end of a set of instructions. We must count the number of pushes and pops. Both should be equal. In the above coding, note that both are equal.

4.7.5 XCH-type Instructions

An XCH instruction is for exchanging the A register with a source using the register (direct or indirect addressing) mode. An XCHD instruction is to exchange the lower hex-digit (nibbles) between the A and RAM using indirect addressing. The 8051 XCH and XCHD instructions are as per Table 4.3.

Table 4.5 XCH and XCHD instructions in 8051

a i = 0 or 1 for a register at a register bank.

b n = 0 or 1 or … or 6 or 7 at a register in register bank.

c If A has 50H and Ri has 7FH and at address 7FH the byte is 42H, then, A will have 42H and at address 7FH the byte will be 50H after the exchange.

The advantage of this XCH instruction is that the accumulator can be temporarily saved at an address and the value used from that address for arithmetic or logical operations. Later, the old value of A can be retrieved and the result after the operation will be back to that address by repeating the exchange instruction. Similarly, the lower digits can be operated and upper digits can be kept intact using the XCHD. For example, in TMOD, the lower digit is for the timer T0. Note that TMOD has to be first taken to the internal RAM address before being used for XCHD since its operand is accessible in the indirect addressing mode only.

Example 4.26

Swap the contents (bytes) at P0 and P1.

Table 4.5 shows that the exchange instructions between the bytes at the direct addresses are not available in 8051. However, XCH A, direct is available. Therefore, the following instructions will swap P0 and P1:

- XCH A, P0 (exchange A and P0 contents).

- XCH A, P1 (when exchanging A and P1 contents, P1 gets contents of original value of P0 through the A. Then, A gets the contents of P1).

- XCH A, P0 (when exchanging A and P0 contents, P0 gets contents of original contents of P1. A gets the contents of P0, which has A’s original value after the first instruction).

4.8 DATA AND BIT-MANIPULATION INSTRUCTIONS

4.8.1 Data Byte Manipulate (Clear, Complement, Rotate and Swap) Instructions

Figure 4.13(a) shows the byte manipulation instructions. These are for clear, complement, rotate and swap A. The source and destination operand addresses are the same and it is only the A (accumulator) that can be manipulated in 8051.

- A CLR instruction makes all bits 0s. A=0000 0000 after CLR A.

- A CPL instruction complements all 1s to 0s and vice versa. For example, if A=A5H=10100101 then after CPL the A=01011010b.

- An RL instruction rotates left. For example, bits 10001010b become 00010101b, and the C flag of PSW also becomes 1 after rotate left.

- An RLC instruction rotates left through the carry flag. For example, consider bits, A=10001010b and C=0. RLC makes A=00010100b and the C flag also becomes 1. After the rotate left through carry the C flag shifts to lsb (least significant bit) at A and msb (maximum significance bit) to C.

- RR and RRC are similar to RL and RLC instructions and are for the rotate right and rotate right through carry.

- RR rotates right and thus shifts lsb to msb and also to C.

- The C flag shifts to msb and the lsb to C in RRC after rotation.

Figure 4.13 (a) Operations in the byte manipulation instructions using A and (b) operations in the Boolean variable manipulation (bit manipulation) instruction using C or a bit at an address of the bit.

- SWAP is for swapping between the upper hex-digit with the lower hex-digit. For example, 89H will become 98H after SWAP.

- The 8051 CLR, CPL RL, RLC, RR, RRC and SWAP instruction features are given in Table 4.6.

Table 4.6 CLR, CPL RL, RLC, RR, RRC and SWAP instructions in 8051

Example 4.27

How do the mode bits of timers 0 and 1 swapped at the TMOD?

TMOD has the lower nibble for the mode of timer 0. TMOD upper nibble is for timer 1 mode. Table 4.6 shows that instruction for swap of nibbles is available for swap in A only.

The following instructions will swap the lower and upper nibbles of modes of timers 0 and 1.

- PUSH 0E0H (for saving A onto the stack).

- MOV A, 89H (equivalent to MOV A, TMOD as 89H is the TMOD direct address).

- SWAP A.

- MOV89H, A.

- POP 0E0H (for restoring the A from the stack).

Example 4.28

What will be the effect of RRC A, assuming A = 02H and C = 1?

The RRC instruction means rotate right through carry. Original carry will move to msb and original lsb into CY. Therefore, C will become 0 as 02H = 0000 0010b in A. The result will be 1000 0001b in A. Therefore, A will now be 81H.

Example 4.29

What will now be the effect of CPL A? Assume that it executes after the RRC in Example 4.28.

The CPL A instruction means complement A. A = 81H at the beginning after the RRC. Therefore, A will become 0111 1110 (7EH) after CPL A.

Complement the port P2 bits.

The 8051 has all the arithmetic and logic operations using the A (accumulator). Table 4.6 shows that there is no complement direct instruction. Port P2 bits can be complemented though the use of A. The instructions will be as follows:

(i) XCH A, P2; (ii) CPL A and (iii) XCH A, P2.

Note that the combination of two instructions (i) and (iii) restores A to the original value. One can also use (i) MOV A, P2; (ii) CPL A and (iii) MOV P2, A. However, this will affect the contents of A.

Example 4.31

How can the bits be rotated using the rotate instruction without affecting C at the end?

Use PUSH 0D0H (equivalent to PUSH PSW) at the start of the rotate instruction and POP PSW at the end.

4.8.2 Boolean Variable (Bit) Manipulate and Boolean Processing Instructions

Figure 4.13(b) shows the bit-manipulation instructions. These are also called Boolean processing instructions. The source or destination operand is either C or bit. The C or bit is clear, set, complement. There can be transfer (copy) or ANDing and ORing using bit and C. C acts like the Boolean accumulator like the A in byte-manipulating instructions.

The bit means bit at a bit address. Refer Table 3.2 for the bit addresses (between the 80H and FFH in select SFRs like P0, P1, …). Refer Figure 3.6 for the bit addresses between 00H and 7FH for 16 bytes at the internal RAM between 20H and 2FH.

- A MOV instruction transfers the bit between C and bit.

- A CLR instruction makes C or bit = 0.

- A CPL instruction complements C or bit. For example, the bit at bit address 93H will be 0, if 1. Note that 93H is for the bit 3 in byte at P1 (Table 3.2).

- A SETB instruction sets C or bit. For example, the bit at bit address BAH = 1b after the SETB. Note that BAH is the address of bit 2 in SFR IP (Table 3.19).

- An ANL instruction does ANDing between C and bit or complement of the bit,

. For example, assume bit at P2 bit 3 (address = B3H) = 1 and C = 0. After ANDing C and bit P2.3, C becomes 0.

. For example, assume bit at P2 bit 3 (address = B3H) = 1 and C = 0. After ANDing C and bit P2.3, C becomes 0. - An ORL instruction does ORing between C and bit or complement of the bit,

. For example, consider bit at RS0 = 0b (address D3H). It is a PSW bit. And C=0. After ORing C and bit PSW.3, C becomes 1.

. For example, consider bit at RS0 = 0b (address D3H). It is a PSW bit. And C=0. After ORing C and bit PSW.3, C becomes 1.

The 8051 MOV, CLR, CPL, SETB, ANL and ORL instruction features are given in Table 4.7. These are the important instructions for setting or clearing the bits, like for the ports, TCON, SCON, A, B, PSW, IP and IF.

Example 4.32

Write instructions (i) P1 port bit 0 = 0, (ii) IE bit 7 = 1 and (iii) Complement TCON bit 6.

We use Table 4.7 instructions for clearing, setting and complementing the bits as follows:

- CLR P1.0 or CLR 90H to clear the bit at the bit address 90H,which is P1.0.

- SETB IE.7 or SETB 0AFH to set the bit at the bit address AFH, which is IE.7.

- CPL TCON.6 or CPL 08EH to complement the bit at the bit address 8EH, which is TCON.6

- CPL 0BH to complement the bit at the bit address 0BH, which is bit 3 at 21H (remember 00H to 07H are the bit addresses for RAM at 20H and 08H to 0FH, the bit addresses for RAM at 21H).

Example 4.33

Complement the bit 3 of internal RAM at 21H.

CPL 0BH. It complements the bit at the bit address 0BH, which is bit 3 at 21H (remember 00H to 07H are the bit addresses for RAM at 20H and 08H to 0FH, the bit addresses for RAM at 21H).

Example 4.34

Move bit 2 of P3 into C.

Consider bit at P3 bit 2 (address B2H) 1 and C 0. After MOV C, 0B2H instruction, C becomes 1. [C is a Boolean processor accumulator.]

Example 4.35

Clear bit 1 at the RAM at 20H.

It means make 0 the bit at bit address 01H. Since 01H has the bit 1 in the RAM byte at 20H, CLR 01H is the instruction.

Example 4.36

Start timer 0 by setting TR0 bit in TCON.

Address for the byte of TCON is 88H, and TR0 at it is bit addressable by the bit address 8CH (Table 3.11). Therefore, the instruction is SETB 8CH to make TR0 = 1.

Table 4.7 MOV, CLR, CPL, SETB, ANL and ORL Boolean processing instructions in 8051

a These operations do not affect the flags unless the destination address bit is at PSW (between D0H and D7H).

Example 4.37

Test whether Port P2 bit 5 is set (=1).

Address for the byte of P2 is A0H, and bit 5 at it is bit addressable by the bit address A5H (Table 3.2). Therefore, the instructions are as follows:

SETB C; ANL C, A5H; if C becomes 1 when instruction executes, then P2.5 is 1, else it is 0.

4.9 ARITHMETIC INSTRUCTIONS

Figure 4.14(a) shows the arithmetic instructions. The instructions are for 8-bit addition, subtraction, increment, decrement, multiply and division instructions. There is a 16-bit DPTR increment (without affecting the flags) instruction. Assume 12 MHz XTAL crystal with 8051, then an instruction cycle has 6 states S1 to S6 and each state has two clock pulses generated by the oscillator. Therefore the cycle time = 1 μs. Multiplication and division then take 4 μs and increment DPTR take 2 μs.

- Add and subtract and increment and decrement instructions. The instruction uses one of the four addressing modes each—register, immediate, direct and indirect.

- There are two sets of addition instructions—add without carry and add with carry. Both use one of the 4 models of addressing. Figure 4.14(b) shows five steps for ADDC A, R3. Step 1: Read C = 1. Step 2: Read 50H at A. Step 3: Read 81H at R3. Step 4: Add 50H, 1 and 81H and Step 5: Put the result D2H in A and since the result is no carry, no auxiliary carry and no overflow, clear the C, AC and OV in PSW.

- There is only one set of subtract instruction—subtract with borrow (C). Subtract without borrow can be done in two steps—CLR C and then SBBB.

- C, OV and AC are affected as follows: C is set when the addition results in answer > FFH and set when subtraction results in the answer < 00H. AC is set when an addition or subtraction in the lower-nibble operation changes the value of the upper-nibble. AC is used for decimal adjusting the result by DA A instruction after the addition. OV is useful in addition or subtraction of the signed numbers.

- Multiplication and division instructions use only the register-addressing mode and use only A and B. OV is affected and is useful in determining whether 8 bits multiplied by 8 bits results in an 8 bit (when OV0) or in 16-bit (when OV 1) number. OV is also useful in determining that denominator was 0 earlier (OV = 1) or not (OV 0) during the division.

- DA A (decimal adjust accumulator) instruction use only the register addressing mode and uses the A.

- INC DPTR instruction has only one addressing mode—16-bit register (pair) addressing mode and uses DPL and DPH.

The 8051 arithmetic ADD, SUB, MUL, DIV, INC and DEC instruction features are given in Table 4.8.

a n is 0 or 1 or … or 6 or 7 for a register in the register bank defined by RS0 and RS1 of PSW SFR.

b OV 1 if there is a carry out of the bit position 6 but not from bit position 7 or if there is a carry out of bit position 7, but not from bit position 6 during subtraction. OV is thus an exclusive OR operation between the carries from bit 6 position and bit 7 position. When OV 1 and C 0, it means that the result becomes above 128 but is below 256. When OV 0 and C 1, it means that the result becomes above 256 with carry from bit position 6 as well as 7. When OV 1 and C 1, it means that the result becomes above 256 with no carry from bit position 6 but carry bit from position 7. Remember that in two’s complement arithmetic, a byte above 127 means overflow in subtraction. (255 means FFH. 256 makes A 0.)

c Direct is the byte for the address from where the byte is to be used in arithmetic operation. Address should be valid (existing SFR) in the SFR area or should be between internal RAM 00H and 7FH. d i = 0 or 1 the byte to be moved from the address pointed by the contents of R.. Prefix implies a pointer register. R0 or R1 is a pointer at a register in a bank. The bank defines by the bits RS0 and RS1 in PSW. e Data mean the byte to be used in arithmetic operation.

f LSB means least significant byte and MSB means maximum significant byte.

g OV sets if the result of multiplication exceeds FFH and higher bits b8-b15 of the result are at B. C always resets to 0.

h Unsigned numbers division, when the radix points of numerator and denominator at the same bit position, OV and C both reset to 0s. The OV sets to 1 when the resulting quotient and remainder are indeterminate (remain undefined in the case when the denominator happens to be zero). In the quotient, the radix point is to the right side of lsb (bit-0) in A. C always resets to 0.

Example 4.38

Add 128 and 129 decimals.

The 128 decimal means 80H and 129 means 81H. Table 4.8 shows that one of the bytes must be placed in A. 8051 ALU needs one of the operands at the accumulator. The instruction will therefore be as follows:

(i) MOV A, #80H (Refer Table 4.1). (ii) ADD A, #81H; the result in A will be 01H and carry will be 1 and OV 1. That means that the result is 256 decimal + 1 = 257 and both additions are of numbers of the same negative sign. The answer is taken as −257 because OV 1.

Example 4.39

Subtract decimal 129 from 128 and then subtract 5 again.

Subtract without borrow is not available in 8051 (Table 4.8). We should first clear carry and then subtract in the first time operation of subtraction of 128 and 129. C (borrow) is likely to generate in the first subtraction, hence in subsequent subtractions, we always use subtract with borrow. Instructions will be as follows:

(i) MOV A, #80H (move 128 decimal in A) [Table 4.1] (ii) CLR C (clear carry which is also for the borrow so that C, set in any previous operation, becomes clear now) (Table 4.7), (iii) SBBB A, #81H (Table 4.8). The result in A will be FFH and carry will be 1 and OV = 0 due to borrow at the 6th as well as the 7th position. This corresponds to −1. Both numbers were of the same negative sign and (iv) SBBB A, 05H (second subtraction). The result will be F9H and C resets to 0 and OV = 0. The result has to be adjusted because it means that both the numbers were of the opposite signs. Therefore, the adjusted result should be considered as −6 and not as −7.

Example 4.41 also shows how we can write assembly instructions in an appropriate format.

Example 4.40

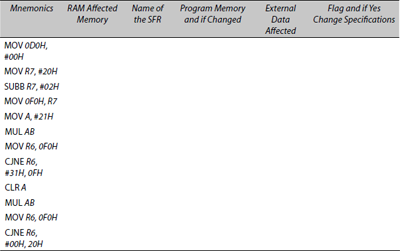

Add 16-bit numbers at R0−R1 (lower byte at R0) with another 16-bit number at R2−R3 (lower byte at R2) and place the result at R4−R5 (lower byte at R4). Let us use the instruction starting at 00A0H. Use Appendix G to specify codes.

Carry flag is needed in the present program because 8-bit addition instructions ADD and ADDC affect C, AC and OV.

; Program Example 4.40

; Uses PSW.7 bit, PSW.6 and PSW.2 (C, AC and OV) and the 8-bit accumulator.

; Raj Kamal August 15, 2009

; Variables at R0 to R5,

; Temporary variables at R6 and R7

; org 0x0A0

4.10 INSTRUCTIONS FOR LOGICAL OPERATIONS ON BYTES AT THE REGISTERS, INTERNAL RAM AND SFRS

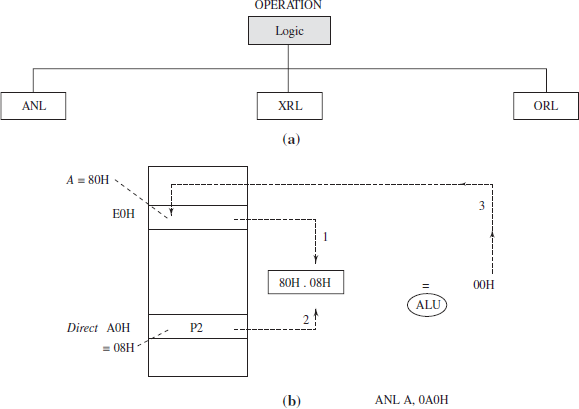

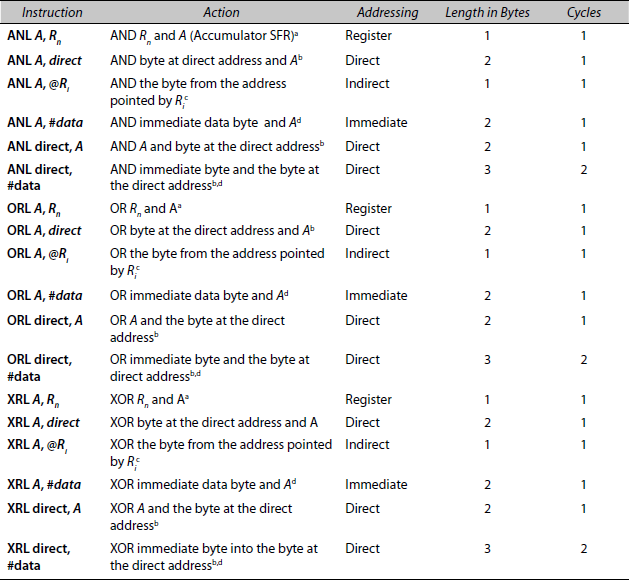

Figure 4.15 (a) shows the operations during the logic instructions. The AND, OR and XOR instructions have four addressing modes each — register, immediate, direct and indirect. When there is a 12-MHz XTAL with 8051, the instruction cycle equals one cycle. Each cycle has six states. One cycle period = 1 μs and is identical for the AND, OR and XOR instructions for register, direct and indirect addressing modes. It is 2 us when the immediate addressing mode for source 2 and the direct for source 1 are used.(Table 4.9)

The 8051 logic ANL, ORL and XRL (and, or and xor logic, respectively) instructions are given in Table 4.9. Figure 4.15(b) shows three steps in the implementation of ANL A, P2. P2 direct address is A0H. Step 1: Read 80H from A (address E 0H). Step 2: Read 08H from P2 (address A0H). Step 3: ALU does logical AND operation between the two. Write the result 00H into A.

Figure 4.15 (a) Operations in the logic instructions and (b) three-step implementation of ANLA, A0H The operations are at addresses E0H and 08H.

Table 4.9 ANL, ORL and XRL instructions in 8051

a n is 0 or 1 or … or 6 or 7 for a register in the register bank defined by RS0 and RS1 of PSW SFR.

b Direct is the byte specifying the address from where the data byte is to be used in arithmetic operation. The address should be valid (existing SFR) in the SFR area or should be between 00H and 7FH RAM.

c i = 0 or 1, the byte to be moved from the address pointed by the contents of Ri. Prefix implies a pointer register. R0 or R1 is a pointer register in a bank. The bank is defined by the bits RS0 and RS1 in PSW.

d Data means the data8 immediate operand of 8 bits used in arithmetic operation.

Example 4.41

Let A = FFH. AND and A the bits at SBUF using an ALU instruction.

We can AND A and the SBUF by the AND operation of A with SBUF using ANL A, direct instruction in row 2 of Table 4.9 as SBUF has a direct address 99H. The instruction will be as follows:

(i) When A = FFH then the instruction to AND A and SBUF is as follows: ANL A,99H (Table 4.9). This is equivalent to ANL A, SBUF.

Example 4.42

Set the bits 7 and 6 at SCON without affecting other bits.

First, set the bits 7 and 6 and reset all the remaining bits in A by MOV A, #data (Table 4.1) and then perform the OR operation of A with SCON. The instructions are:

(i) ORL SCON, #C0H. All bit except the 6th and 7th = 0s.

Example 4.43

How can we start timers 0 and 1 at the same instance?

Refer Table 3.11; Timers 1 and 0 start when TR1= 1 and TR0 = 0. TR1 and TR0 are TCON 6th and 4th bits. TCON address is 88H. Instruction will be as follows:

(i) ORL 88H, #50H; after the instruction executes, bits at TCON are ORed with 01010000. All except the 6th and 4th bits = 0s (Table 4.1) 88H, A.

Example 4.44

How can we toggle the bits at Port 2? (Make P2 bits = 1s as 0s and 0s as 1s). Table 3.2 gives the Port 2 direct address is A0H. An XOR operation with 1 makes a bit 0 if previously 1 and makes it 1 if previously 0. Therefore, if P2 is XORed with = all 1s (= FFH) and then use of the XOR instruction for toggling bits.

(i) XRL P2, #0FFH toggles the bits at P2 at direct address A0H.

Example 4.45

Use ANL, ORL and XRL instructions for the bytes for clearing, setting and complementing the specific bits.

- TCON register bit 7 is to be cleared. TMOD bits are not addressable by the bit addresses.

Therefore the instruction is:

ANL TCON, #7FH; AND with 0111 1111b to clear bit 7 (msb)

- SCON register bit 0 is to be set. The instruction is:

SCON, #01H; OR with 0000 0001 to set bit 0 (lsb)

- A register bit 6 is to be complemented. The instruction is as follows:

XRL A, # 40H; XOR A with 0100 0000 to complement bit 6 (msb but1)

- R0 register bit 2 is to be complemented. There is no XRL instruction, which has R0 as destination The instructions are as follows:

- MOV A, R0; Move R0 into A to enable XOR operation between 2 bytes

- XRL A, #04H; XOR A with 0000 0100b to complement bit 2

- MOVR0, A; Move back changed into R0 from A.

4.11 PROGRAM-FLOW CONTROL INSTRUCTIONS

Program-flow instructions change the program flow from sequential order. The instructions for jump, call and reset instructions are called program flow instructions. They change the program counter to a value other than the one present after the increment of program counter just after an instruction fetch. A program may have the while or for loop. It may have the conditions for executing a specific section of the instructions. A program may jump to another address in case of executing a conditional instruction or while-loop or repeat loop. The program may call other routine(s) in between the instructions. The routine may return to calling routine or program at the end of the instructions. These actions warrant a change in the program-flow path. The program counter after steadily incrementing after each code of the instruction acquires a new value to start another program-flow path.

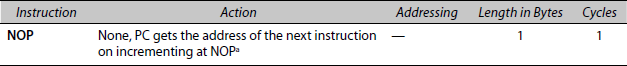

4.11.1 Delay-cycle (NOP) Instructions

The 8051 has NOP instruction. It means no operation, just spent one instruction cycle time.

a For a XTAL of frequency 12 MHz, the cycle consists of 1 us because 1 cycle has six states S1 to S6 and each state has two pulses.

Suppose a port pin connects to a driving transistor. The transistor drive the current in the speaker. We can program delays for sending 1s and 0s. The delay intervals depen on the musical note sent to the speaker. The musical notes are played successively in a song.

Example 4.46

How can we toggle the bits at Port 2 and again toggle after a delay of 10 μs? (Make the bits = 1s as 0s and 0s as 1s. Delay 10 μs. Again make 1s as 0s and 0s as 1s.)

Refer Example 4.44. Assume that XTAL oscillation frequency = 12 MHz. We introduce the delay of 10 us using 8 NOPs. Then repeat XOR operation with P2 after the NOPs. Instructions will be as follows:

(i) XRL 0A0H, #FFH (XRL with all bits = 1s) (equivalent to XRL P2, #11111111b as direct address of P2 is A0H) (ii) to NOP; NOP; NOP; NOP; NOP; NOP; NOP; NOP; (x) XRL P2, #FFH.

Eight NOPs for 10 μs because of one instruction cycle time each spent in NOP instructions and XRL P2 takes 2 cycles, there is a 10 instruction cycle time which is spent, thus there is delay of total next address 10 μs.

4.11.2 Long, Absolute and Short Jumps

The 8051 has three jump instructions—jump to any 16-bit address, jump to address within the 2 kB space and jump to the address within 128 bytes above or below the present address. These are called long, absolute and short jumps. Table 4.10 gives the jump instructions and the cycles taken for operations.

Table 4.10 Long, absolute and short jump instructions in 8051

a 16-bit address in long jump (LJMP)—Instruction Opcode bits = 8.

b Jump within the next 2 kB address space of the currently executed program (of program memory); the five highest significant bits are unchanged in the PC in absolute jump (AJMP). Instruction Opcode bits = 5.

c rel is a signed number and a signed 8-bit number has the decimal value between −128 and +127. Instruction Opcode bits = 8.

d 16-bit address is indirectly found. JMP-instruction Opcode bits are 8.

Figure 4.16 shows the operations for the—AJMP Addr11instruction. Figures 4.16 shows that 5 upper bits from PCH are the 5 msb in the 16-bit memory address. Three upper bits in the first byte of AJMP instruction are next 3 bits after 5 msb in 16-bit memory address. Eight bits in the second byte of AJMP instruction are 8 bits after 8 msb in the 16-bit memory address. It means the second byte of AJMP instruction transfers to lsb 8-bits in a new value of PC. (It also means that this byte transfers to PCL.)

Example 4.47

Jump to a program memory address after 8 kB addresses (2000H addresses) from the location of the next instruction, which is 1000H.

The jump is above 2 kB code space (Table 4.10). We can, therefore, use only the jump long. Now, 1000H + 2000H = 3000H. Therefore, the instruction is as follows: LJMP 3000H.

Example 4.48

Jump to a program memory address after 16 addresses backwards from the location of the next instruction, which is 1000H.

Jump is relative and is to less than 256 locations (Table 4.10). We can, therefore, use the jump short. Now −16 decimal = F0H. [Two’s complement number of 16d is FOH]. Therefore, instruction is as follows: (i) SJMP 0F0H.

Example 4.49

Jump to a program memory location after 16 locations backwards relative to the DPTR contents. Jump is relative and backward but using DPTR (Table 4.10). We can, therefore, use the JMP @A + DPTR. Now −16 decimal = F0H. Therefore, the instructions are as follows:

- MOV A, #0F0H

- JMP @A + DPTR

Example 4.50

Jump to a program memory address after 1000 locations from the beginning of current instruction. Jump is within the 2 kB code space (Table 4.10). We, can, therefore, use jump absolute. Since jump takes place not from the current but from the next instruction after the jump instruction and jump absolute instruction length = 2 bytes, jump has to be after 1022B. The 11 bits for 1022 decimal = 011 1111 1110. The 5-opcode bits are the lower bits opcode of AJMP is 00001 and 011 for the needed for higher bits. Therefore, the instructions will be as follows:

Figure 4.16 Operations during the jump instruction—AJMP Addr11

AJMP 0FEH; (with 1st byte = 61H and 2nd byte = FEH) (Table 4.10)

4.11.3 Conditional Short Relative Jumps

The 8051 has seven conditional jump instructions and these are given in Table 4.11. The table also gives the cycles taken during the operations of these control instructions.

Table 4.11 Conditional short relative-jump instructions in 8051

Note: rel is a signed number and a signed 8-bit number has the decimal value between −128 and +127. Instruction opcode bits = 8.

Example 4.51

If SCON.4 (serial receiver enable) = 1, then jump to a program memory location which is 32 locations back-wards from the location of next instruction. Next instruction is at 1040H. Reset carry also.

Refer Table 3.16. SCON.4 bit address = 9CH. Jump is relative and is within 256 locations. Refer Table 4.11. We can, therefore, use the conditional jump short. Now −32 decimal = E0H [Two’s complement number of 32 is E0H]. Therefore, the instruction is as follows:

(i) JBC 9CH, 0E0Hat the address 103DH. (Note: When assembling, we use 0E0H for E0H by convention).

Example 4.52

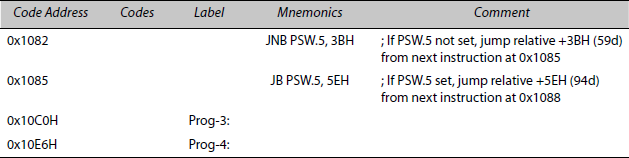

Execute program-3 instructions from memory location 0x10C0 if input at the user flag F0 = 0, else program-4 from 0x10E6. Let the present program addresses start from 1082H.

: Program Example 4.52

: Exemplary use of the JNB and PSW and F0 bits in the instructions

: Variable declaration—Boolean PSW.5 (F0 is at PSW.5)

: Org 1082H

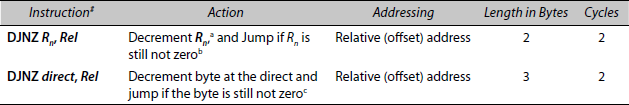

4.11.4 Decrement and Conditional Jump on Zero

The 8051 has two instructions for decrement the register and direct. There is conditional jump if the decrement does not result in all bits at register or direct address = 0s. These instructions are extremely valuable in case of the looping. There is exit from the loops after executing a certain number of loops. Table 4.12 gives the instructions. The table also gives the cycles taken for the operations of the instructions.

Table 4.12 Instruction for decrement and then jump in program loops in 8051